Le spécialiste du stockage Sandisk vient de recruter des experts pour élaborer sa stratégie sur la HBF (high bandwith flash). Cette technologie doit compléter la HBM très utilisée dans les infrastructures IA.

Dans le domaine des mémoires pour les infrastructures IA, la technologie HBM (high bandwith memory) est devenue incontournable. Elle est utilisée dans les GPU et certains CPU pour serveurs pour fournir un accès extrêmement rapide aux données, bien plus qu’avec de la DRAM standard. Mais une autre architecture commence à apparaître sous le nom de HBF (high bandwith flash) promue par Sandisk.

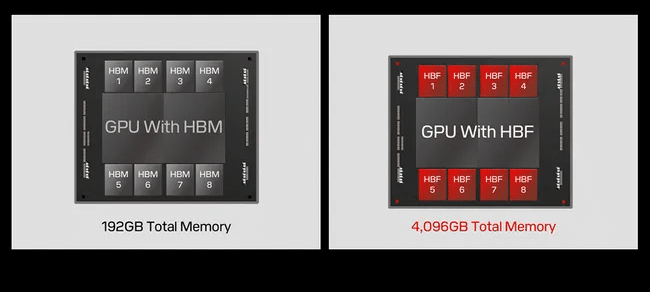

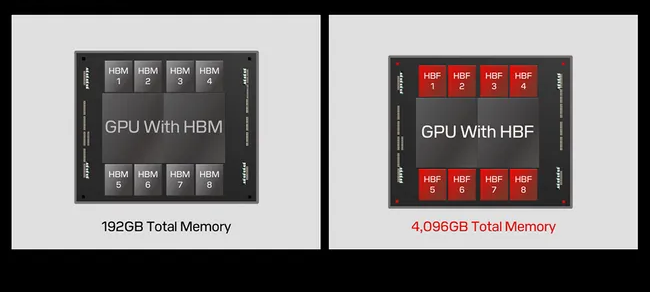

Le spécialiste de la mémoire a donné quelques indications en février dernier via Alper Ilkbahar vice-président des technologies mémoires chez Sandisk. « L’approche est de diviser la matrice de mémoire de la NAND en plusieurs mini matrices et accéder à chacune d’entre elles en parallèle ». Il ajoute, « ces mini-matrices peuvent être empilées en vertical en s’appuyant sur la technologie BICS 3D-NAND de Kioxia. Nous l’avons utilisé pour des mémoires de R&D de 16 couches avec des capacités de 8 à 16 fois supérieurs aux HBM pour un prix similaire ». Sandisk a déjà démontré comment un GPU IA utilisant uniquement la HBM pouvait prendre en charge 192 Go de mémoire, mais en le combinant avec la HBF, ce chiffre pourrait atteindre 3 To. Dans une configuration utilisant uniquement la HBF, la capacité de mémoire pourrait atteindre 4 To.

Le gain de capacité mémoire avec la HBF est important selon Sandisk. (Crédit Photo: Sandisk)

Un comité techniques avec des experts pour convertir les fournisseurs de GPU

Mais pour promouvoir la HBF, Sandisk a besoin de convertir aussi les fournisseurs de GPU pour fournir des interfaces. En sachant que Nvidia et SK Hynix promeuvent conjointement la HBM tout comme Micron et Sasmung, la société doit impérativement trouver des relais auprès des autres acteurs de l’IA. Dans ce cadre, elle vient de créer un comité technique en nommant des personnalités influentes comme le professeur David Patterson et Raja Koduri. Le premier est le co-développeur de RISC (reduced instruction set computing) et a joué un rôle important dans le RAID (redudant array of inexpensive disks). Dans un communiqué, il explique que « le HBF promet de jouer un rôle important dans l’IA des centres de données en offrant une capacité de mémoire sans précédent à haut débit, permettant ainsi aux charges de travail d’inférence de dépasser largement les contraintes actuelles. Cela pourrait réduire les coûts des récentes applications d’IA qui sont actuellement inabordables ».

De son côté, Raja Kodury a occupé le poste d’architecte en chef chez AMD où il a dirigé le développement des architectures GPU Polaris, Vega et Navi. Il a par ailleurs était vice-président des systèmes accélérés et graphiques chez Intel où il a piloté la création des GPU Arc et Ponte Vecchio. Pour lui, la HBF va « révolutionner l’usage de l’IA en edge en équipant les terminaux d’une capacité de mémoire et d’une bande passante capables de supporter des modèles sophistiqués en local et en temps réel ».