La conférence Hot Chips 2025 (du 24 au 26 août à Palo Alto) a servi de toile de fond au tout dernier processeur Xeon d’Intel, le Clearwater Forest, entièrement composé de coeurs E, et première puce fabriquée avec la technologie de gravure 18A du fondeur.

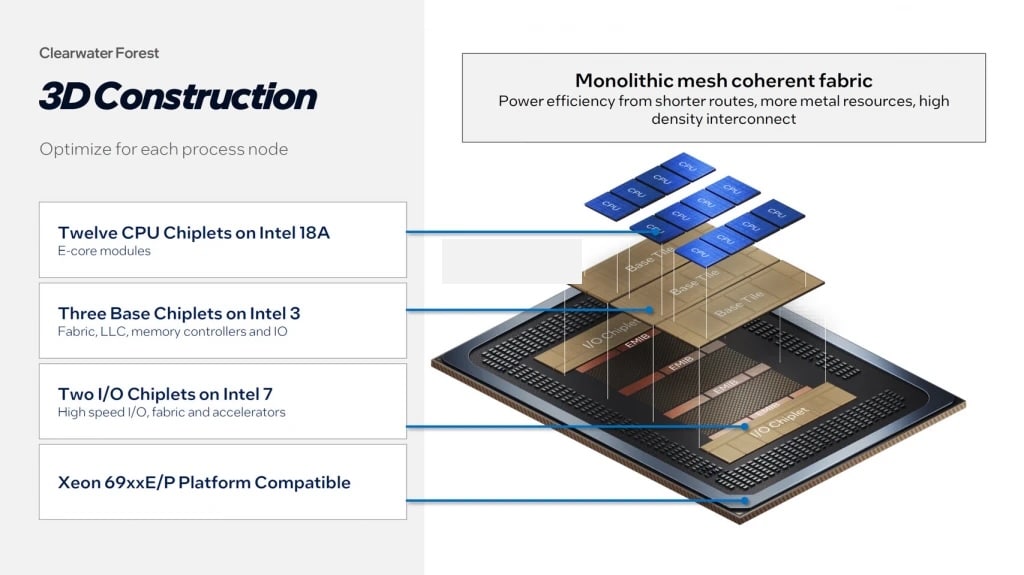

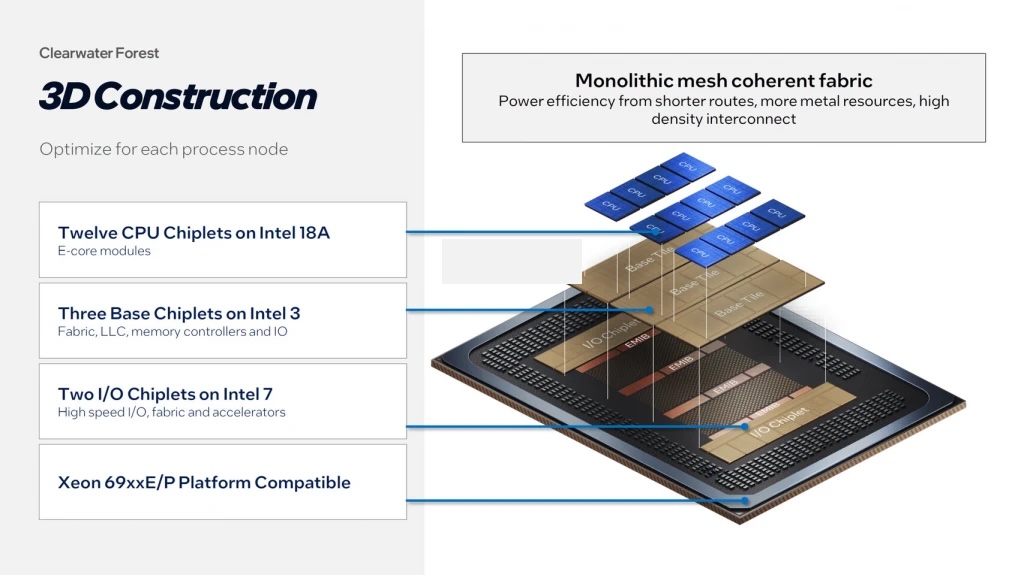

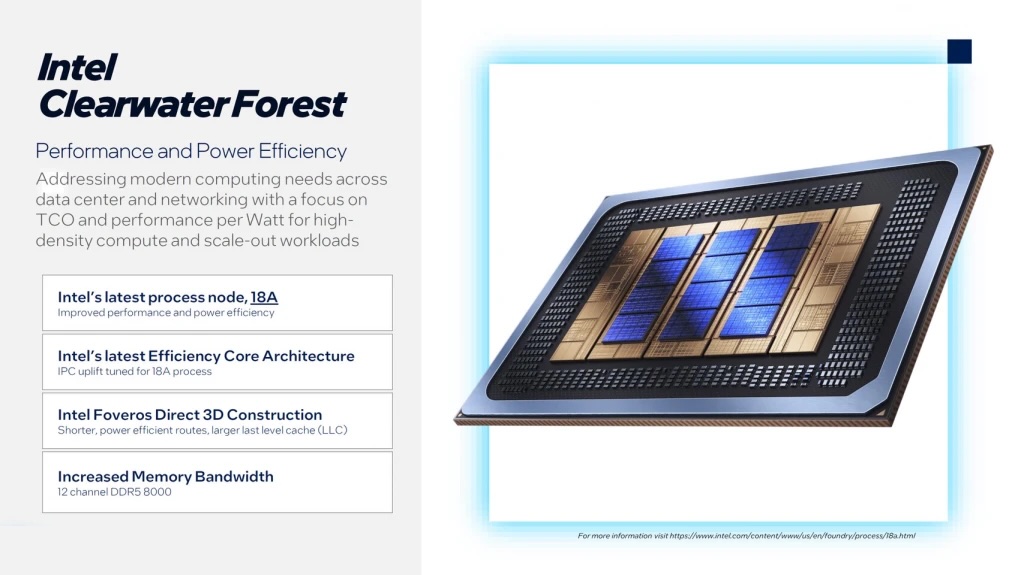

Conférence annuelle qui se tient chaque année sur le campus de l’université de Stanford – l’alma mater de nombreux talents de la Silicon Valley, dont Pat Gelsinger et Jensen Huang – Hot Chips, du 24 au 26 août cette année, est une immersion totale dans la technologie des puces, animée par une multitude d’ingénieurs en électricité qui discutent entre eux, sans aucun responsable marketing à l’horizon. Intel en a profité pour dévoiler son processeur Xeon Clearwater Forest, qui devrait être commercialisé en 2026 et sera l’un des premiers gravés en 18A (1,8 nm), la prometteuse technologie développée par le fondeur depuis 2021 avec la stratégie 5 nœuds en 4 ans promue à l’origine par Pat Gelsinger. Précisons que seule la partie pour la partie coeurs CPU sere gravée en 18A, le bloc mémoire reposera encore sur une gravure Intel3 et le bloc IO sur Intel7 dans le cadre d’une architecture chiplets.

Comme ses concurrents, Intel exploite plusieurs finesses de gravure pour composer les différentes parties de sa puce Xeon Clearwater Forest. (Crédit Intel)

Ce Xeon Clearwater Forest intègre 288 cœurs Efficiency (E-cores) et succède à la puce Sierra Forest à 144 cœurs actuellement sur le marché. Ces dernières années, Intel a modifié la conception de ses processeurs pour passer à des cœurs Efficiency (E-cores) et Performance (P-cores). Leurs noms décrivent bien ce qu’ils sont : de type basse consommation, les E-cores sont moins puissants et moins performants, et sont conçus pour des tâches simples, tandis que les P-cores sont plus complexes, plus puissants et consomment plus d’énergie. La plupart des puces Xeon exploitent des P-cores, mais Clearwater Forest s’annonce différente. Bien qu’il s’agisse d’une évolution de l’architecture Sierra Forest, elle repose sur une conception de cœurs Efficiency offrant des performances plus élevées. Quatre cœurs partagent 4 Mo de cache L2, et la puce double la bande passante L2 par rapport à la conception Sierra. Selon Intel, cette puce excellera dans les applications multithread telles que l’inférence IA.

Pour montrer qu’il n’est pas encore complètement dépassé, Intel a annonce au dernier Hot Chips sa puce Xeon Clearwater Forest. (Crédit Intel)

Les sous-systèmes d’alimentation ont également été considérablement remaniés, améliorant la densité et l’efficacité de la signalisation. Combiné au processus de fabrication 18A, cela devrait aider Intel à combler l’écart de performances dont AMD a tant profité grâce à ses conceptions plus efficaces, avec jusqu’à 192 coeurs (Zen 5/Zen 5c) sur ses puces serveurs Epyc 9965 fabriquées en 3 nm chez TSMC. Cela ne veut pas dire qu’il n’y aura pas également des améliorations considérables en termes de performances sur les Xeon Clearwater Forest. Dans un serveur bisockets, la puce proposera 24 lignes pour la mémoire DDR5 8000 avec une bande passante de 1,3 Tb/s, 192 voies PCIe Gen 5 ainsi que de 64 voies de connectivité CXL, et 576 cœurs avec 1 152 Mo de cache combiné pour 59 TF/s.